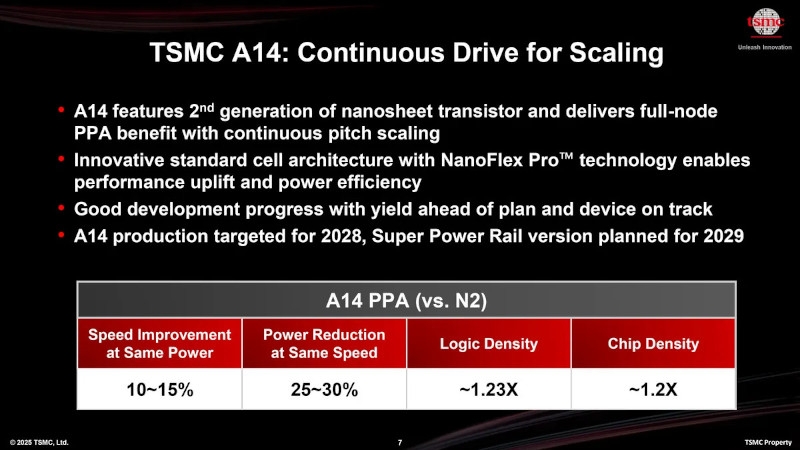

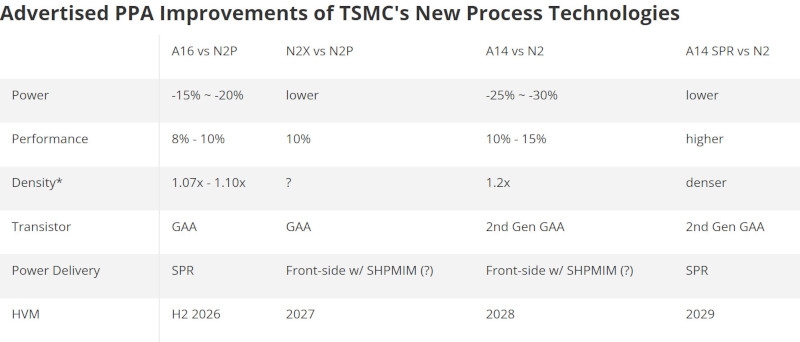

TSMC анонсировала 1,4-нм техпроцесс A14 на транзисторах Gate-All-Around (GAA) второго поколения. Технология обеспечит прирост производительности на 10–15 % при том же энергопотреблении, а также снижение потребляемой мощности на 25–30 % при сохранении частоты и логической сложности по сравнению с 2-нм N2. Плотность логических элементов повысится на 23 %, а общая плотность транзисторов в условиях смешанного проектирования — 20 %. Массовое производство запланировано на 2028 год, а версия с подачей питания с обратной стороны чипа дебютирует в 2029 году.

Во время Североамериканского технологического симпозиума, компания TSMC сообщила, что A14 — это новый техпроцесс, разработанный с нуля, так что для него не подойдут дизайны чипов, спроектированные для предыдущих техпроцессов. Новая технология построена на транзисторах с нанолистами (nanosheets) второго поколения, произведённых с использованием новейшей технологии GAA. Это отличает его от техпроцесса N2P, основанного на платформе N2, и от A16, представляющего собой улучшенный N2P с системой подачи питания с обратной стороны (Backside Power Delivery — BSPDN). В отличие от A16, базовая версия A14 не поддерживает архитектуру Super Power Rail. Это снижает стоимость, но ограничивает применение технологии в сценариях, где требуется высокая плотность разводки электропитания. Однако отсутствие BSPDN делает A14 целесообразным выбором для тех приложений, в которых преимущества этой технологии минимальны или не проявляются.

Несмотря на отсутствие BSPDN, техпроцесс A14 сохраняет высокую эффективность благодаря использованию транзисторов с нанолистами второго поколения. Одним из ключевых компонентов технологии является NanoFlex Pro — усовершенствованная архитектура стандартных ячеек, предоставляющая разработчикам гибкость при конфигурировании логических блоков с учётом трёх важных метрик: производительности, энергопотребления и площади кристалла (Power, Performance, Area — PPA). Хотя компания не раскрывает технических отличий NanoFlex Pro от предыдущей версии NanoFlex, можно предположить, что речь идёт о расширенных возможностях DTCO — совместной оптимизации проектирования и технологии — а также более точной настройке на уровне ячеек и транзисторов.

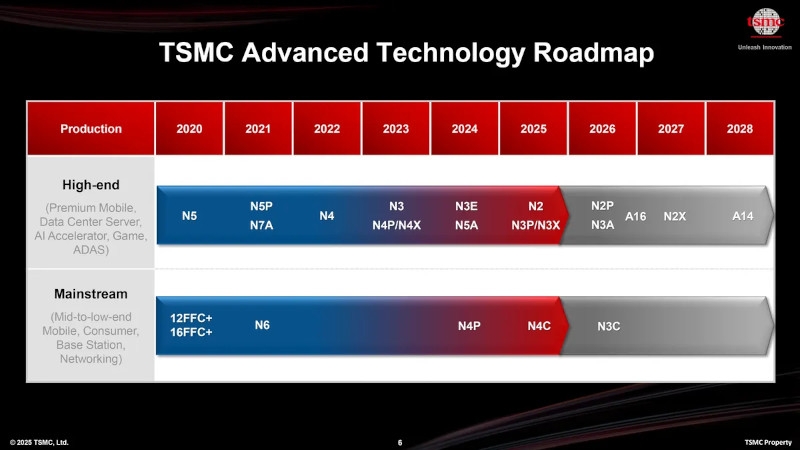

TSMC ожидает, что массовое производство чипов по технологии A14 начнётся в 2028 году. При этом компания пока не уточнила, в каком полугодии начнётся серийный выпуск этих чипов. Учитывая, что массовое производство по техпроцессам N2P и A16 начнётся во второй половине 2026 года, можно предположить, что производство чипов по технологии A14 будет приурочено к первой половине 2028 года. Версия A14 с архитектурой Super Power Rail (SPR) — системой подачи питания с обратной стороны микросхемы (BSPDN) — ожидается в 2029 году. Хотя официальное название этой модификации пока не объявлено, вероятно, оно будет соответствовать принятой номенклатуре TSMC и получит обозначение A14P.

Особенностью A14 остаётся использование системы подачи питания с лицевой стороны, аналогичной применяемой в техпроцессах N2 и N2P. Это делает архитектуру особенно уместной в клиентских и специализированных вычислительных задачах, где не требуется высокоплотная разводка линий питания, но критичны энергоэффективность и масштабируемость.

По информации TSMC, техпроцесс A14 ориентирован на широкий спектр применений, включая клиентские устройства и задачи периферийных вычислений, где важна высокая производительность при ограничениях по энергопотреблению и площади кристалла. Благодаря архитектурным особенностям и параметрам, технология A14 обеспечивает сбалансированность по ключевым метрикам PPA в различных сценариях проектирования.